#

## Quantum Capacitance Limited Vertical Scaling of Graphene Field-Effect Transistor

Huilong Xu, Zhiyong Zhang,\* Zhenxing Wang, Sheng Wang, Xuelei Liang, and Lian-Mao Peng\*

Key Laboratory for the Physics and Chemistry of Nanodevices and Department of Electronics, Peking University, Beijing 100871, China

raphene has extremely high intrinsic carrier mobility and ultralong mean free length<sup>1-4</sup> and has therefore been considered as one of the most promising candidates to replace the silicon channel in metal-oxide-semiconductor (MOS) field-effect transistors (FETs) with superior performance to extend Moore's Law in future nanoelectronics.<sup>4,5</sup> Since FET is a capacitance-operated device in which the conductance between source and drain is modulated by the gate, the gate insulator is among of the most crucial elements determining the performance of the FET device. To maintain sufficient gate control on the conduction channel during the lateral dimension scaling down in order to improve performance and integrated density of integrated circuits (ICs), the distance between the gate and channel will be simultaneously scaled down; that is, a thinner and thinner gate oxide is required to improve the drain-current response of the transistor to the applied gate voltage and to avoid short channel effect.<sup>6</sup> Unfortunately, similar to other two-dimensional (2D) electron gas FET system,<sup>7</sup> the vertical scaling down in the graphene FET cannot be continued forever and the total gate capacitance in a FET device with a very thin gate oxide is ultimately limited by the current leakage via gate and quantum capacitance originated from the finite density of states of the channel and the extra energy needed to pump electrons to states with higher energy.<sup>8,9</sup> To explore the limit of vertical scaling of graphene FETs, an ultrathin insulator with very high-quality and large capacitance must be fabricated on top of graphene at first. Although there exist several methods for fabricating a high-quality and uniform insulating layer on graphene,<sup>10-16</sup> an extremely large gate capacitance that is comparable to quantum capacitance has not been

**ABSTRACT** A high-quality  $Y_2O_3$  dielectric layer has been grown directly on graphene and used to fabricated top-gate graphene field-effect transistors (FETs), and the thickness of the dielectric layer has been reduced continuously down to 3.9 nm with an equivalent oxide thickness (EOT) of 1.5 nm and excellent insulativity. By measuring CV characteristics of two graphene FETs with different gate oxide thicknesses, the oxide capacitance and quantum capacitance are retrieved directly from the experimental CV data without introducing any additional fitting process and parameters, yielding a relative dielectric constant of  $\kappa = 10$  for  $Y_2O_3$  on graphene and an oxide capacitance of about 2.28  $\mu F/cm^2$ . It is found that for a rather large gate voltage range, this oxide capacitance is comparable and sometimes even larger than the quantum capacitance of graphene. Since the total gate capacitance is determined by the smaller of the oxide and quantum capacitance, our results show that not much further improvement can be gained *via* further vertical scaling down of the gate oxide, suggesting that  $Y_2O_3$  may be the ultimate dielectric material for graphene. It is also shown that the  $Y_2O_3$  gate dielectric layer with EOT of 1.5 nm may also satisfy the ultimate lateral scaling requirement on the gate length of graphene FET and be used effectively to control a graphene FET with a gate length as small as 1 nm.

**KEYWORDS:** graphene field-effect transistor · quantum capacitance · yttrium oxide · gate dielectric · vertical scaling

achieved in solid-state graphene devices, and the vertical scaling behavior of graphene FETs down to their quantum limits has not been investigated.

From a fundamental point of view, accurate measurement of quantum capacitance of graphene also provides an important tool for exploring the density of state or electronic compressibility of the material. Recently, quantum capacitance of graphene was measured and then retrieved by several groups in solid-state graphene devices,<sup>17-19</sup> but only few accurate results were obtained that can be compared directly to theory. This is because in most cases a high-quality insulator layer cannot be grown readily on pristine graphene. To solve this problem, some functionalization or buffering layers were introduced before growing a high-k dielectric layer on graphene.<sup>10–14</sup> The additional buffer layers, however, would significantly reduce the total oxide capacitance, which is usually

\* Address correspondence to zyzhang@pku.edu.cn, Impeng@pku.edu.cn.

Received for review January 4, 2011 and accepted January 30, 2011.

Published online February 16, 2011 10.1021/nn200026e

JAr

www.acsnano.org

© 2011 American Chemical Society

VOL.5 • NO.3 • 2340-2347 • 2011

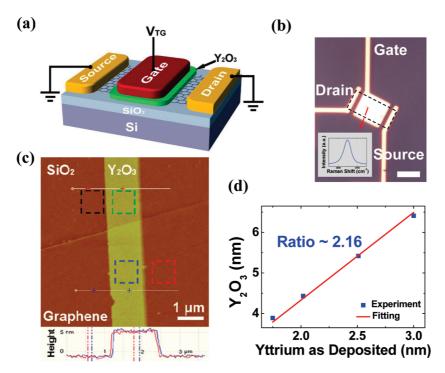

Figure 1. Single-layer graphene FET integrated with  $Y_2O_3$  top-gate dielectric. (a) Schematics of the graphene device and experiment setup, where the graphene  $-Y_2O_3$  - Ti/Au capacitor stack lies on a SiO<sub>2</sub>/Si substrate. (b) Typical optical image showing the as-fabricated graphene FET device. The graphene sheet is marked by the dashed frame, and the channel area covered by the top gate is  $W = 4.5 \ \mu$ m and  $L = 7 \ \mu$ m. The separation between source/drain electrodes to the top-gate electrode is 1.2  $\mu$ m. The scale bar denotes 5  $\mu$ m. Inset: typical Raman spectrum (with an excitation laser with wavelength 633 nm) of the graphene sample used in our device, suggesting the sample is a single-layer graphene. (c) Top: AFM topographic images showing an  $Y_2O_3$  film on SiO<sub>2</sub> and single-layer graphene. The surface roughness values ( $\sigma$ ) of SiO<sub>2</sub> (marked by dashed black square),  $Y_2O_3$  on SiO<sub>2</sub> (marked by dashed green square), graphene on SiO<sub>2</sub> (marked by dashed red square), and  $Y_2O_3$  on graphene (marked by blue square) are 230, 308, 238, and 295 pm, respectively. The scale bar of the topographic image is 1  $\mu$ m. Bottom: the height profiles of the  $Y_2O_3$  film (measured *via* AFM) as a function of the nominal thickness of the as-deposited Y film (measured directly using the crystal sensor in the deposition system).

far smaller than corresponding quantum capacitance, and as a result, the quantum capacitance cannot be accurately retrieved due to its very small contribution to the total gate capacitance. On the other hand, by using ionic liquid<sup>20</sup> as the gate insulator, the gate dielectric layer thickness can be reduced down to the subnanometer region where the quantum capacitance of graphene starts to dominate. However, an ion-rich environment introduces tremendous disturbances even at regions far from the Dirac point, and an unexpected strong asymmetric capacitance behavior was often observed.<sup>20</sup> Very recently, the capacitance and density of states of graphene were measured under varying electrical and magnetic field,<sup>21</sup> but the oxide capacitance is still much smaller than the quantum capacitance of the graphene.

In an earlier work, we reported that high-quality  $Y_2O_3$  films can be uniformly grown on graphene *via* evaporating yttrium (Y) film followed by thermal oxidation.<sup>22</sup> In this article, we will demonstrate that the thickness of the  $Y_2O_3$  film can be precisely controlled and shrunk continuously to improve the gate capacitance of the graphene FET. The oxide and quantum capacitances are retrieved directly from measured C-V curves without introducing any additional fitting

XU ET AL.

parameters, and the retrieved oxide capacitance from C-V measurements is then compared with that by DC transport measurements. The obtained quantum capacitance of the graphene FET is found to typically account for more than 50% of the total gate capacitance and agrees excellently well with theory. In general, the gate capacitance improvement from vertical scaling down will become less effective and ultimately be limited by the quantum capacitance when the effective gate oxide layer thickness (EOT) is reduced to be less than a few nanometers. The thinnest Y<sub>2</sub>O<sub>3</sub> film fabricated in this work has an EOT of 1.5 nm, which is shown to satisfy the requirement for efficient gate control for a graphene FET with a gate length down to 1 nm.

#### **RESULTS AND DISCUSSION**

We first consider the fabrication and characterization of the graphene FETs used for our following capacitance measurements. Figure 1a depicts the geometry of a top-gate graphene FET, and Figure 1b shows an optical microscope image of a real device. Atomic force microscopy (AFM) measurements (Figure 1c) show that the fabricated Y<sub>2</sub>O<sub>3</sub> film is uniform over a large area and introduces hardly any additional roughness on graphene. The thickness of the Y<sub>2</sub>O<sub>3</sub> film is

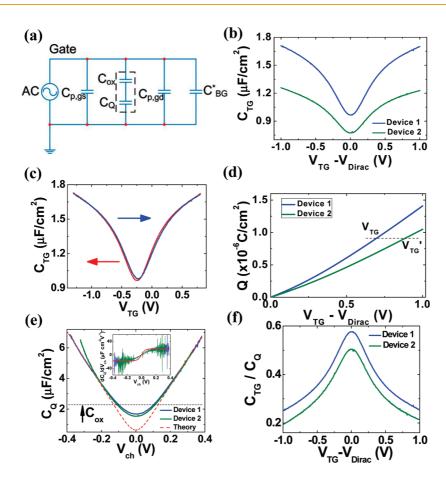

Figure 2. Measurement and retrieval of quantum capacitance of graphene FETs. (a) High-frequency equivalent circuit of a topgate graphene FET for CV measurement. (b) Experimental total gate capacitances of graphene FETs with Y<sub>2</sub>O<sub>3</sub> dielectric layer thicknesses of 3.9 nm (blue curve, device 1) and 5.6 nm (green curve, device 2), respectively. (c) Total gate capacitance curves measured by sweeping gate voltage from negative (positive) to positive (negative), showing little hysteresis behavior of the total gate capacitance in our graphene FETs with Y<sub>2</sub>O<sub>3</sub> thickness of 3.9 nm. (d)  $V_{TG}$  dependent *Q* obtained for devices 1 and 2 by integrating the  $C_{TG} - V_{TG}$  curves in panel b. (e) Theoretical and experimental quantum capacitance as a function of the channel voltage  $V_{ch}$ . The red dashed curve is the theoretical value for graphene at 300 K, with the Fermi velocity being 1.15 × 10<sup>6</sup> m/s. The horizontal dashed line is the oxide capacitance of device 1. Inset: experimental and calculated  $dC_Q/dV_{ch}$  as a function of  $V_{ch}$ . (f) Capacitance ratios between the total gate capacitance and quantum capacitance as a function of top-gate voltage.

linearly proportional to the as-deposited thickness of the evaporated Y film with a ratio of about 2.16 (Figure 1d). The total gate capacitance was measured between the gate electrode and the graphene channel beneath it with one electrode of the capacitor being the gate electrode and the other being the common terminal of source and drain. To guarantee the accuracy of the capacitance measurement, a graphene sheet larger than 50  $\mu$ m<sup>2</sup> was used to fabricate the FET device. The area of the graphene beneath the top gate is thus large enough to ensure that the measured capacitance (typically larger than 200 fF in our devices) is larger than the measurement limit (typically smaller than 1 fF) of the instrument. In general, the measured capacitance  $C_{M}$  contains contributions from the top gate and other parasitic capacitances as shown in Figure 2a and can be modeled as

$$C_{\rm M} = C_{\rm TG} + C_{\rm p,gs} + C_{\rm p,gd} + C_{\rm BG}^{*}$$

(1)

where  $C_{TG}$  is the total gate capacitance to be measured,  $C_{p,gs}$  ( $C_{p,gd}$ ) is the parasitic capacitance between the

XU ET AL.

top-gate and source (drain) electrode, and  $C^*_{BG}$  is the parasitic capacitance originated from the back gate (but not the back-gate capacitance). The total contribution due to all parasitic capacitances was estimated by carrying out a measurement on a device with identical geometry but without the graphene channel beneath the top-gate dielectric. This contribution was found to be on the order of 1 fF and is negligible compared to the top-gate capacitance of our graphene devices, which is typically larger than 200 fF. To a good approximation, we may thus neglect the effect due to the parasitic capacitance to use  $C_{M} \approx C_{TG}$ .

The gate voltage dependent capacitances ( $C_{TG}$ - $V_{TG}$ ) for two typical graphene FETs (denoted as devices 1 and 2) with Y<sub>2</sub>O<sub>3</sub> gate dielectric layer thicknesses of 3.9 and 5.6 nm, respectively, are shown in Figure 2b. Three distinct features are presented in these  $C_{TG}$ - $V_{TG}$  curves. (1) Almost perfect symmetry for electron and hole branches is observed centered at Dirac point, reflecting the symmetric band structure for electron and hole in graphene.<sup>2,3</sup> (2) The hysteresis is smaller

VOL.5 • NO.3 • 2340-2347 • 2011

than 30 mV in the  $C_{TG} - V_{TG}$  curve for different sweeping directions as shown in Figure 2c, suggesting that there exists few charge traps in the Y<sub>2</sub>O<sub>3</sub> film or at the interface between  $Y_2O_3$  and graphene. (3) The value of  $C_{TG}$  is seen to have increased by about 80% in changing the gate voltage from the Dirac point toward both positive (electron branch) and negative (hole) regions with a magnitude of  $\pm 1$  V. This tremendous change of  $C_{\rm TG}$  may be attributed to the change of the quantum capacitance under varying gate potential. In principle, we can thus pick up ample information about the quantum capacitance of graphene from the  $C_{TG} - V_{TG}$ curve.

The total gate capacitance can be modeled as a series of oxide capacitance and quantum capacitance (Figure 2a), that is

$$C_{\text{TG}}^{-1}(V_{\text{TG}}) = C_{\text{Q}}^{-1}(V_{\text{ch}}) + C_{\text{OX}}^{-1}$$

(2)

where  $C_{OX}$  is the oxide capacitance of the top gate, which is hardly dependent on  $V_{TG}$ , and  $C_Q$  is the quantum capacitance of graphene, which is dependent on  $V_{TG}$  via the graphene channel potential  $V_{ch}$ . The quantum capacitance can be extracted from the measured gate capacitance C<sub>TG</sub> using eq 2 straightforwardly for any gate voltage  $V_{TG}$ :

$$C_{\rm Q}(V_{\rm ch}) = \frac{C_{\rm OX}C_{\rm TG}(V_{\rm TG})}{C_{\rm OX} - C_{\rm TG}(V_{\rm TG})}$$

(3)

where

$$V_{\rm ch} = V_{\rm TG} - \int_{0}^{V_{\rm TG}} C_{\rm TG} / C_{\rm OX} dV_{\rm TG}^{'}$$

is the integral form of  $C_{TG} dV_{TG} = C_{OX} d(V_{TG} - V_{ch})$ , which results from charge conservation.

Since the growth of dielectric film on graphene is usually different from that on other substrates even with the same growth condition, the relative dielectric constant  $\kappa$  of the Y<sub>2</sub>O<sub>3</sub> film on graphene may differ from that on silicon or other substrates. Since the directly measured C<sub>TG</sub> includes inevitably the contribution of the quantum capacitance of graphene, the problem of retrieving  $\kappa$  value (or oxide capacitance) from CV measurements is not a trivial one. Two popular methods are widely used. The first is to fit experimental CV curves,<sup>21</sup> and the second is simply to use experiential value.<sup>17-20</sup> In this paper, we utilize the fact that in our experiments we can control the thickness of the Y<sub>2</sub>O<sub>3</sub> film on graphene. We can therefore determine both the quantum capacitance of graphene and the relative dielectric constant of Y<sub>2</sub>O<sub>3</sub> film simultaneously via measuring  $C_{TG}-V_{TG}$  curves for two devices (Figure 2b) with different gate oxide thicknesses (for details see part I of Supporting Information).

We can eliminate the Q dependent  $C_0$  far away from the Dirac point (for example with  $|V_{ch}|$  larger than 0.2 V) and obtain the value of  $\kappa$ , which is about 10 here. Using this k value, the oxide capacitances can be estimated to be 2.28 and 1.56  $\mu$ F/cm<sup>2</sup>, respectively, for the two devices with Y<sub>2</sub>O<sub>3</sub> thicknesses of 3.9 and 5.6 nm. The  $V_{\rm ch}$  dependent quantum capacitance  $C_{\rm O}$  can be retrieved by subtracting the oxide capacitance Cox from the total gate capacitance  $C_{TG}$  by eq 3. The retrieved channel potential V<sub>ch</sub> dependent C<sub>Q</sub> values are shown in Figure 2e. It should be noted that the quantum capacitance near the Dirac point varies from sample to sample, which may be attributed to the different residue charges induced by charged impurities on graphene or in surroundings.<sup>20,21,23–27</sup>

The extracted C<sub>Q</sub> from experimental measurements on two devices with different dielectric layer thicknesses has an ideal quantum capacitance which may be fitted using<sup>9</sup>

$$C_{\rm Q} = \frac{2q^2kT}{\pi(\hbar v_{\rm F})^2} \ln \left[ 2 \left( 1 + \cosh \frac{qV_{\rm ch}}{kT} \right) \right]$$

(4)

where the Fermi velocity  $v_{\rm F}$  is found to be 1.15  $\times$  10<sup>6</sup> m/s, which agrees excellently well with that reported by other groups.<sup>21,28-31</sup> It is obvious that the experimental Co results are well in agreement with theory except for these points near the Dirac point (Figure 2e). The quantum capacitance  $C_Q$  is seen to increase linearly with V<sub>ch</sub> in regions far away from the Dirac point with a slope of 18  $\mu$ F cm<sup>-2</sup> V<sup>-1</sup>, but the slope becomes much smaller and begins to deviate from theoretical value near the Dirac point, as shown in the inset of Figure 2e. Since the density of state at the Dirac point is dominated by electron-hole puddles induced by charged impurities around the graphene channel,<sup>26,27,31,32</sup> it is expected that the quantum capacitance should depart from theoretical values near the Dirac point, which is similar to that of the channel conductivity behavior near the Dirac point.

For an extremely thin gate dielectric layer, the quantum capacitance contributes not just a small correction to the total gate capacitance, instead it begins to dominate over the conventional oxide capacitance  $C_{OX}$ . We compared the larger  $C_{OX}$  (device 1) with retrieved  $V_{ch}$  dependent  $C_Q$  in Figure 2e, demonstrating clearly that for a large  $V_{ch}$  range (~0.2 V)  $C_{OX}$  is larger than  $C_Q$ . The contribution of the quantum capacitance to the total gate capacitance may be represented using the ratio  $C_{TG}/C_{O}$ , and the resulting  $C_{\rm TG}/C_{\rm O}-V_{\rm TG}$  curve is shown in Figure 2f. This figure shows clearly that the contribution of quantum capacitance accounts for more than 20% of the total gate capacitance for the whole  $V_{TG}$  range from -1 to +1 V, and the contribution increases up to 58% at the Dirac point for device 1 and about 50% for device 2. For a  $V_{TG}$ range between -0.2 and 0.2 V, the ratio is always larger than 50%, showing that C<sub>O</sub> is dominating the total gate capacitance in our device 1.

While CV measurements can provide information on both oxide capacitance and quantum capacitance, the oxide capacitance C<sub>OX</sub> can also be obtained by DC

VOL. 5 • NO. 3 • 2340-2347 • 2011

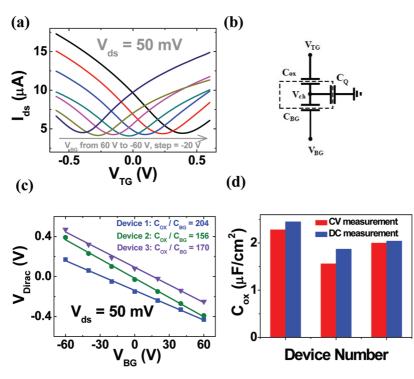

Figure 3. DC measurements and statistics on graphene FETs. (a) Typical gate transfer characteristics of a graphene FET, showing the shift of the Dirac point of the top-gate transfer characteristic at different back-gate voltage. (b) Equivalent capacitive circuit of a graphene FET that is being controlled by both the top gate and back gate simultaneously. (c) Top-gate voltage at the Dirac point as a function of the back-gate voltage. The triangles, circles, and squares are experiment data of three different devices, and solid lines are linear fittings of the experimental data. The inverse of the slope of the solid line gives the capacitance ratio  $C_{OX}/C_{BG}$ , where  $C_{BG} = 0.0121 \,\mu$ F/cm<sup>2</sup>, being the capacitance of the back gate with a SiO<sub>2</sub> thickness of 287 nm. (d) Comparison of oxide capacitances retrieved from DC measurement and AC results for the three devices.

measurements.<sup>11,15,16,33</sup> Since the graphene channel may be simultaneously controlled by top gate and back gate, the Dirac point voltage  $V_{\text{TG,Dirac}}$  in the top-gate transfer characteristic can be modulated by back-gate voltage  $V_{\text{BG}}$  (Figure 3a). Using the capacitive equivalent circuit scheme of the dual-gate graphene FET, as shown in Figure 3b,<sup>34</sup> it can be shown (see part II of Supporting Information) that the shift in the top-gate Dirac point voltage  $\Delta V_{\text{TG,Dirac}}$  is linearly dependent on the change in the back-gate voltage  $\Delta V_{\text{BG}}$  as

$$C_{\rm OX}/C_{\rm BG} = -\Delta V_{\rm BG}/\Delta V_{\rm TG,Dirac}$$

(5)

The shifts in the top-gate Dirac point  $V_{TG,Dirac}$  as a function of back-gate voltage  $V_{BG}$  are shown in Figure 3c for three different graphene FETs and fitted using eq 5. From the slope of the fitted line, we can readily read out the ratio between the oxide capacitance of the back gate and top gate. Since the back-gate capacitance is known, the top-gate oxide capacitance can therefore be obtained without any prior knowledge on the quantum capacitance. The slope of the  $V_{BG}-V_{TG,Dirac}$  curves (Figure 3c) reflects the top/back-gate ratio, that is, top-gate relative (to back-gate) efficiency, and for the three devices, we investigated the efficiencies of, respectively, 204, 156, and 170. It should be noted that these top-gate relative efficiencies are far beyond all of the previous published

values.<sup>11,12,15,16,33</sup> Using the back-gate capacitance of 0.0121  $\mu$ F/cm<sup>2</sup> (for a SiO<sub>2</sub> layer with a thickness of 287 nm and relative dielectric constant of 3.9, measured by ellipsometer), the top-gate capacitances of the three graphene FETs investigated are, respectively, 2.47, 1.89, and 2.06  $\mu$ F/cm<sup>2</sup>. We compared these oxide capacitances from DC transfer curves with those retrieved from CV measurements in Figure 3d, which shows good agreements of the results obtained through independent methods. The slight deviation may come from the imprecise estimation of the backgate capacitance without considering the depletion layer capacitance of lightly doped silicon substrate or fluctuation in the thickness/relative dielectric constant in DC method, and in principle, the deviation is further magnified by top-gate efficiencies (about 200 times) when the top-gate oxide capacitances were calculated from these values. Carrier mobility is another key parameter for top-gated graphene FET with a high-k insulator. We can extract mobility for device 1 from the transfer curves shown in Figure 3a using a model described in ref 11 (see also Figure S1 and part III of Supporting Information). The retrieved electron and hole mobilities are, respectively, 1900 and 1800 cm<sup>2</sup>/ V·s. In principle, the carrier mobility of the top-gated graphene devices can be further improved through optimizing the quality of the Y<sub>2</sub>O<sub>3</sub> film by improving oxidization temperature.

VOL.5 • NO.3 • 2340-2347 • 2011

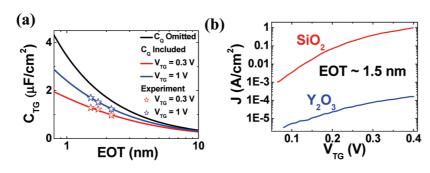

Figure 4. Vertical scaling behavior of graphene FETs. (a) Total gate capacitance with (dark blue for  $V_{TG} = 1$  V and red for  $V_{TG} = 0.3$  V) and without (black) the effect of quantum capacitance of graphene being taken into consideration. Solid curves denote theoretical calculations, and stars represent experiment results. (b) Gate leakage current density of a graphene FET with an Y<sub>2</sub>O<sub>3</sub> layer thickness of 3.9 nm (corresponding to EOT  $\sim$  1.5 nm) vs that of silicon MOS structure. The data of SiO<sub>2</sub> are adapted from Figure 2 of ref 35.

To estimate the limit performance or ultimate potential of graphene FETs, we now explore the vertical scaling behavior of the graphene FET where the quantum capacitance is expected to play an important role. The influence of the quantum capacitance on the total gate capacitance  $C_{TG}$  is shown in Figure 4a, and our measurements on three samples agree well with the theoretical predictions. It is clear that the improvement on  $C_{TG}$  via down scaling or reducing the gate dielectric layer thickness is becoming less effective with reducing equivalent oxide thickness (EOT) which is defined as

$$EOT = \frac{\varepsilon_{SiO_2}}{\kappa} t_{ox}$$

(6)

where  $\varepsilon_{SiO_2}$  = 3.9 and  $\kappa$  = 10 are, respectively, the relative dielectric constants of the silicon oxide and Y<sub>2</sub>O<sub>3</sub> on graphene. The smallest EOT realized in our graphene FETs is about 1.5 nm, which corresponds to the gate oxide EOT employed in the 45 nm silicon CMOS technology for low power circuits.<sup>35</sup> When  $V_{TG}$  = 1 V, where  $C_Q$  is relatively large, the total gate capacitance is reduced by  $(C_{OX} - C_{TG})/C_{OX} = 26\%$  as a result of quantum capacitance. This reduction becomes even more severe for smaller EOT or  $V_{TG}$ . When  $V_{TG}$  is reduced to 0.3 V, the reduction in the total capacitance is increased up to 44%. Therefore, the benefit of increasing the total gate capacitance via vertical scaling down will become less effective for thinner oxide owing to the limit imposed by the quantum capacitance of graphene.

It should be noted that EOT of 1.5 nm achieved here is the thinnest gate dielectric layer in all published graphene FETs. One important question that one would like to ask is how small a graphene FET could be given that we can now control the graphene channel *via* a top gate with an EOT of 1.5 nm. For a FET with planar channel geometry, such as a singlegated SOI MOSFET, the screening length  $\lambda$  is the key parameter for estimating the ultimate gate length and is given by<sup>36,37</sup>

$$\lambda = \sqrt{\frac{\varepsilon_{\text{bulk}} t_{\text{bulk}} t_{\text{ox}}}{\varepsilon_{\text{ox}}}}$$

(7)

cita (7) me par

in which  $\varepsilon_{\text{bulk}} = 1^{38}$  and  $t_{\text{bulk}} = 0.3 \text{ nm}^{39}$  are, respectively, relative dielectric constant and thickness of a single-layer graphene, and  $\varepsilon_{ox} = \kappa = 10$  and  $t_{ox} = 3.9$  nm are relative dielectric constant and thickness of Y2O3 gate insulator. Using these values in eq 7, we can then estimate the screening length to be about  $\lambda = 0.34$  nm. Since the actual gate length should be approximately three times larger than  $\lambda$ ,<sup>36,37</sup> the ultimate gate length of the graphene FET can thus be estimated to be about 1 nm for a gate dielectric layer with EOT of 1.5 nm. It is well-known that a FET device with a gate length of 1 nm must become invalid due to the tremendous direct tunneling current between source and drain; in reality, the gate length of graphene FET cannot be reduced down to 1 nm. We therefore conclude that an Y<sub>2</sub>O<sub>3</sub> gate dielectric layer with EOT of 1.5 nm will be sufficient for graphene FETs with any reasonable scaled gate length, and in principle, it is not necessary to further improve the gate capacitance via reducing EOT.

In principle, the gate efficiency can still be improved by perhaps 10% *via* further reducing the gate dielectric layer thickness, but the price one has to pay is the increased leakage, which is another important parameter in oxide scaling. The gate leakage current density of our graphene FET is measured and shown in Figure 4b, showing clearly an approximately exponent dependence on gate voltage. The advantage of using high- $\kappa$  dielectric material is amply demonstrated in Figure 4b. The leakage current curve through the Y<sub>2</sub>O<sub>3</sub> gate dielectric layer with an EOT of 1.5 nm is found to be almost 3 orders of magnitude smaller than that through a thermally grown SiO<sub>2</sub> layer with the same EOT.<sup>35,40</sup>

#### CONCLUSIONS

In conclusion, the thickness of  $Y_2O_3$  film has been shrunk continuously to improve the gate capacitance in graphene FET, and the thinnest EOT of about 1.5 nm with excellent insulativity has been integrated in graphene FET. The oxide capacitance and quantum capacitance are simultaneously retrieved from experimental *CV* curves without introducing any fitting parameters, and the retrieved oxide capacitances from

*CV* measurement are compared with that from DC transport measurements. Excellent agreement between the two results is found. Meanwhile, the quantum capacitance of graphene is precisely retrieved from total gate capacitance and found to agree per-

fectly with theory. It is shown that the gate capacitance improvement from vertical scaling down will become less effective, and the gate capacitance will be dominated by quantum capacitance when the thickness of the  $Y_2O_3$  dielectric layer is reduced below 4 nm.

#### **METHODS**

Graphene was deposited by mechanical exfoliation of Kish graphite on silicon substrate, which was covered with a 287 nm thick SiO<sub>2</sub>. The silicon substrate with high resistivity up to 18  $k\Omega \cdot cm$  was used in order to reduce parasitic capacitance in AC measurement. Single-layer graphene samples were identified by optical contrast and Raman spectroscopy. To calculate the gate area precisely, the graphene was first tailored to a rectangle by electron beam lithography (EBL) and reactive ion etching (RIE). The gate was patterned by electron beam lithography, and then a thin uniform yttrium (Y) film was deposited by e-beam evaporation (EBE). The thickness of the Y film was detected by crystal oscillator sensor in the EBE system. The Y film was oxidized at 180  $^\circ\text{C}$  in air, and a uniform yttrium oxide film was then formed on graphene. An additional forming gas  $(Ar/H_2 =$ 5:1) annealing at 300 °C for 1 h in a furnace was carried out before source/drain and gate metal fabrication, so as to improve the dielectric quality of  $Y_2O_3$  and reduce interface states between graphene and  $Y_2O_3$ . The accurate thickness and roughness of the final Y2O3 film on graphene were measured by atomic force microscope (AFM), as shown in Figure 1c. Source, drain, and gate electrodes were then formed through EBL, electron beam evaporation of Ti/Au film with a thickness of 5/45 nm, and followed by a standard lift-off process. All electrical measurements reported in this work were carried out by a probe station (Lakeshore TTP-4) in vacuum and at room temperature. DC transport measurements were carried out using a Keithley 4200 semiconductor analyzer and C-V measurements by an Agilent 1500 B with a small AC modulation (30 mV and 50 kHz). Under C-V measurements, the Si substrates were electrically separated from the chunk of probe station to reduce the substrate-relative parasitic capacitance.

Acknowledgment. This work was supported by the Ministry of Science and Technology of China (Grant Nos. 2011CB933001 and 2011CB933002), the Fundamental Research Funds for the Central Universities, and National Science Foundation of China (Grant Nos. 61071013 and 60971003).

*Supporting Information Available:* Additional experimental details. This material is available free of charge *via* the Internet at http://pubs.acs.org.

#### NOTE ADDED AFTER ASAP PUBLICATION

This paper was published on February 16, 2011 with an error in the y-axis of Figure 4b. The corrected version was reposted on March 22, 2011.

### **REFERENCES AND NOTES**

- Novoselov, K. S.; Geim, A. K.; Morozov, S. V.; Jiang, D.; Zhang, Y.; Dubonors, S. V.; Grigorieva, I. V.; Firsov, A. A. Electric Field Effect in Atomically Thin Carbon Films. *Science* 2004, 306, 666–669.

- 2. Geim, A. K.; Novoselov, K. L. The Rise of Graphene. *Nat. Mater.* **2007**, *6*, 183–191.

- Castro Neto, A. H.; Guinea, F.; Peres, N. M. R.; Novoselov, K. S.; Geim, A. K. The Electronic Properties of Graphene. *Rev. Mod. Phys.* 2009, *81*, 109–162.

- Schwierz, F. Graphene Transistor. Nat. Nanotechnol. 2010, 5, 487–496.

- International Technology Roadmap for Semiconductors (2007 Edition and 2008 Update), http://public.itrs.net/.

- Frank, D. J.; Dennard, R. H.; Nowak, E.; Solomon, P.; Taur, Y. Device Scaling Limits of Si MOSFETs and Their Application Dependencies. *Proc. IEEE* 2001, *89*, 259–288.

- Vasileska, D.; Schroder, D. K.; Ferry, D. K. Scaled Silicon MOSFET's: Degradation of the Total Gate Capacitance. *IEEE Trans. Electron Devices* **1997**, *44*, 584–587.

- Luryi, S. Quantum Capacitance Devices. *Appl. Phys. Lett.* 1988, *52*, 501–503.

- 9. Fang, T.; Konar, A.; Xing, H.; Jena, D. Carrier Statistics and Quantum Capacitance of Graphene Sheets and Ribbons. *Appl. Phys. Lett.* **2007**, *91*, 092109.

- Wang, X. R.; Tabakman, S. M.; Dai, H. J. Atomic Layer Deposition of Metal Oxides on Pristine and Functionalized Graphene. J. Am. Chem. Soc. 2008, 130, 8152–8153.

- Kim, S.; Nah, J.; Jo, I.; Shahrjerdi, D.; Colombo, L.; Yao, Z.; Tutuc, E.; Banerjee, S. Realization of a High Mobility Dual-Gated Graphene Field-Effect Transistor with Al<sub>2</sub>O<sub>3</sub> Dielectric. *Appl. Phys. Lett.* **2009**, *94*, 062107.

- Farmer, D. B.; Chiu, H.-Y.; Lin, Y.-M.; Jenkins, K. A.; Xia, F. N.; Avouris, P. Utilization of a Buffered Dielectric To Achieve High Field-Effect Carrier Mobility in Graphene Transistors. *Nano Lett.* **2009**, *9*, 4474–4478.

- Lee, B. K.; Park, S.-Y.; Kim, H.-C.; Cho, K. J.; Vogel, E. M.; Kim, M. J.; Wallace, R. M.; Kim, J. Y. Conformal Al<sub>2</sub>O<sub>3</sub> Dielectric Layer Deposited by Atomic Layer Deposition for Graphene-Based Nanoelectronics. *Appl. Phys. Lett.* **2008**, *92*, 203102.

- Williams, J. R.; DiCarlo, L.; Marcus, C. M. Quantum Hall Effect in a Gate-Controlled p-n Junction of Graphene. *Science* 2007, 317, 638–641.

- Liao, L.; Bai, J. W.; Qu, Y. Q.; Lin, Y. C.; Li, Y. J.; Huang, Y.; Duan, X. F. High-κ Oxide Nanoribbons as Gate Dielectrics for High Mobility Top-Gated Graphene Transistors. *Proc. Natl. Acad. Sci. U.S.A.* **2010**, *107*, 6711–6715.

- Liao, L.; Bai, J.; Cheng, R.; Lin, Y. C.; Jiang, S.; Huang, Y.; Duan, X. Top-Gated Graphene Nanoribbon Transistors with Ultrathin High-k Dielectrics. *Nano Lett.* **2010**, *10*, 1917–1921.

- Chen, Z.; Appenzeller, J. Mobility Extraction and Quantum Capacitance Impact in High Performance Graphene Field-Effect Transistor Devices. *IEEE IEDM Tech. Digest* 2008, 21.1, 509–512.

- Giannazzo, F.; Sonde, S.; Raineri, V.; Rimini, E. Screening Length and Quantum Capacitance in Graphene by Scanning Probe Microscopy. *Nano Lett.* **2009**, *9*, 23–29.

- Dröscher, S.; Roulleau, P.; Molitor, F.; Studerus, P.; Stampfer, C.; Ensslin, K.; Ihn, T. Quantum Capacitance and Density of States of Graphene. *Appl. Phys. Lett.* **2010**, *96*, 152104.

- Xia, J.; Chen, F.; Li, J. H.; Tao, N. J. Measurement of the Quantum Capacitance of Graphene. *Nat. Nanotechnol.* 2009, 4, 505–509.

- Ponomarenko, L. A.; Yang, R.; Gorbachev, R. V.; Blake, P.; Katsnelson, M. I.; Novoselov, K. S.; Geim, A. K. Density of States and Zero Landau Level Probed through Capacitance of Graphene. *Phys. Rev. Lett.* **2010**, *108*, 136801.

- Wang, Z. X.; Xu, H. L.; Zhang, Z. Y.; Wang, S.; Ding, L.; Zeng, Q. S.; Yang, L. J.; Pei, T.; Liang, X. L.; Gao, M.; Peng, L.-M. Yttrium Oxide as a Perfect High-k Gate Dielectric for Carbon-Based Electronics. *Nano Lett.* **2010**, *10*, 2024–2030.

VOL.5 • NO.3 • 2340-2347 • 2011

- 23. Zhang, Y. B.; Brar, V. W.; Girit, C.; Zettl., A.; Crommie, M. F. Origin of Spatial Charge Inhomogeneity in Graphene. *Nat. Phys.* **2009**, *5*, 722–726.

- Tan, Y.-W.; Zhang, Y.; Bolotin, K.; Zhao, Y.; Adam, S.; Hwang, E. H.; Sarma, S. D.; Stormer, H. L.; Kim, P. Measurement of Scattering Rate and Minimum Conductivity in Graphene. *Phys. Rev. Lett.* **2007**, *99*, 246803.

- 25. Chen, J. H.; Jang, C.; Adam, S.; Fuhrer, M. S.; Williams, E. D. Charged-Impurity Scattering in Graphene. *Nat. Phys.* **2008**, *4*, 377–381.

- Adam, S.; Wang, E. H.; Galitski, V. M.; Darma, S. D. A Selfconsistent Theory for Graphene Transport. *Proc. Natl. Acad. Sci. U.S.A.* 2007, *104*, 18392–18397.

- Hwang, E. H.; Adam, S.; Sarma, S. D. Carrier Transport in Two-Dimensional Graphene Layers. *Phys. Rev. Lett.* 2007, 98, 186806.

- Zhang, Y. B.; Tan, Y. W.; Stormer, H. L.; Kim, P. Experimental Observation of the Quantum Hall Effect and Berry's Phase in Graphene. *Nature* 2005, 438, 201–204.

- Yang, L.; Deslippe, J.; Park, C. H.; Cohen, M. L.; Louie, S. G. Excitonic Effects on the Optical Response of Graphene and Bilayer Graphene. *Phys. Rev. Lett.* **2009**, *103*, 186802.

- Trevisanutto, P. E.; Giorgetti, C.; Reining, L.; Ladisa, M.; Olevano, M. *Ab Initio* GW Many-Body Effects in Graphene. *Phys. Rev. Lett.* 2008, 101, 226405.

- Martin, J.; Akerman, N.; Ulbricht, G.; Lohmann, T.; Smet, J. H.; Klitzing, K. V. Observation of Electron—Hole Puddles in Graphene Using a Scanning Single-Electron Transistor. *Nat. Phys.* 2008, *4*, 144–148.

- Victor, M. G.; Shaffique, A.; Sarma, S. D. Statistics of Random Voltage Fluctuation and the Low-Density Residual Conductivity of Graphene. *Phys. Rev. B* 2007, *76*, 245405.

- Meric, I.; Han, M. Y.; Young, A. F.; Ozyilmaz, B.; Kim, P.; Shepard, K. L. Current Saturation in Zero-Bandgap, Top-Gated Graphene Field-Effect Transistors. *Nat. Nanotechnol.* **2008**, *3*, 654–659.

- 34. Datta, S. *Quantum Transport: Atom to Transistor*; Cambridge University Press: London, 2005; p172.

- Robertson, J. High Dielectric Constant Gate Oxides for Metal Oxide Si Transistors. *Rep. Prog. Phys.* 2006, 69, 327– 396.

- 36. Appenzeller, J. Carbon Nanotubes for High-Performance Electronics-Progress and Prospect. *Proc. IEEE* **2008**, *96*, 201–211.

- Yan, R. H.; Ourmazd, A.; Lee, K. F. Scaling the Si MOSFET: From Bulk to SOI to Bulk. *IEEE Trans. Electron Devices* 1992, 39, 1704–1710.

- Bolotin, K. I.; Ghahari, F.; Shulman, M. D.; Stormer, H. L.; Kim, P. Observation of the Fractional Quantum Hall Effect in Graphene. *Nature* 2009, *462*, 196–199.

- Blake, P.; Hill, E. W.; Neto, A. H. C.; Novoselov, K. S.; Jiang, D.; Yang, R.; Booth, T. J.; Geim, A. K. Making Graphene Visible. *Appl. Phys. Lett.* 2007, *91*, 063124.

- 40. Lo, S.-H.; Buchanan, D. A.; Taur, Y.; Wang, W. Quantum-Mechanical Modeling of Electron Tunneling Current from the Inversion Layer of Ultra-Thin-Oxide nMOSFETs. *IEEE Electron Device Lett.* **1997**, *18*, 209–211.